インテル高位合成コンパイラー プロエディション

製品情報

| 製品名 | インテル高位合成コンパイラー プロエディション |

|---|---|

| バージョン | 22.4 |

| 発売日 | 19年2022月XNUMX日 |

| 廃止通知 | インテル高位合成コンパイラーは、 バージョン 23.4 以降では非推奨です。 |

製品使用説明書

入門ガイド

- コンパイラ環境を初期化します。

- Review 様々なデザイン例ampIntel HLS コンパイラーに付属するファイルとチュートリアル。

ユーザーガイド

- ユーザーガイドには、

- Intel FPGA 製品向けに設計された知的財産 (IP) の合成、検証、シミュレーション。

- コンポーネントとテストベンチの作成から、Intel Quartus Prime ソフトウェアを使用したコンポーネント IP の大規模システムへの統合まで、コンポーネントの開発フロー全体を実行します。

ベストプラクティスガイド

ベスト プラクティス ガイドでは、HLS コンポーネントの FPGA 領域の使用率とパフォーマンスを向上させるために適用できるテクニックとプラクティスが提供されています。コンポーネントの機能の正確性を確認した後、これらのベスト プラクティスを適用してください。

リファレンスマニュアル

リファレンスマニュアルでは、インテルHLSコンパイラーでサポートされている機能に関するリファレンス情報を提供します。インテルHLSコンパイラーのコマンドオプション、ヘッダーの詳細をご覧ください。 fileプラグマ、属性、マクロ、宣言、引数、およびテンプレート ライブラリ。

インテル® 高位合成コンパイラー プロ・エディション バージョン 22.4 リリースノート

- Intel® High Level Synthesis Compiler Pro Edition リリースノートには、Intel High Level Synthesis Compiler Pro Edition バージョン 22.4 に関する最新情報が記載されています。

Intel HLS コンパイラーの廃止予定

- 最新の FPGA 高レベル設計機能、最適化、開発ユーティリティへのアクセスを維持するには、既存の設計を移行して Intel oneAPI Base Toolkit を使用します。

- Intel High Level Synthesis (HLS) コンパイラは、バージョン 23.4 以降では廃止される予定です。

- 移行に関するアドバイスについては、Intel oneAPI 製品ページをご覧ください。ご質問やご要望については、Intel High Level Design コミュニティ フォーラムをご覧ください。

インテルHLSコンパイラー・プロ・エディションのドキュメント・ライブラリーについて

- インテル HLS コンパイラー プロ・エディションのドキュメントは、いくつかの出版物に分かれています。次の表を使用して、探しているインテル HLS コンパイラー プロ・エディションの情報が記載されている出版物を見つけてください。

表1. インテル高位合成コンパイラー プロ・エディション ドキュメント・ライブラリ

| タイトルと説明 | |

| リリースノート

Intel HLS コンパイラーに関する最新情報を提供します。 |

リンク |

| 入門ガイド

コンパイラー環境を初期化して再実行する方法を学び、インテルHLSコンパイラーを使い始めましょう。view様々なデザイン例ampIntel HLS コンパイラーに付属するファイルとチュートリアル。 |

リンク |

| ユーザーガイド

Intel FPGA 製品用に設計した IP (知的財産) の合成、検証、シミュレーションに関する手順を説明します。コンポーネントとテストベンチの作成から、Intel Quartus Prime ソフトウェアを使用したコンポーネント IP の大規模システムへの統合まで、コンポーネントの開発フロー全体を実行します。 |

リンク |

| ベストプラクティスガイド

HLS コンポーネントの FPGA 領域の使用率とパフォーマンスを向上させるために適用できるテクニックとプラクティスを提供します。通常、これらのベスト プラクティスは、コンポーネントの機能の正確性を確認した後に適用します。 |

リンク |

| リファレンスマニュアル

インテルHLSコンパイラーでサポートされている機能に関するリファレンス情報を提供します。インテルHLSコンパイラーのコマンドオプション、ヘッダーの詳細を参照してください。 fileプラグマ、属性、マクロ、宣言、引数、およびテンプレート ライブラリ。 |

リンク |

インテルコーポレーション。 全著作権所有。 Intel、Intel ロゴ、およびその他の Intel マークは、Intel Corporation またはその子会社の商標です。 インテルは、インテルの標準保証に従って、FPGA および半導体製品の性能を現在の仕様に合わせて保証しますが、予告なしにいつでも製品およびサービスを変更する権利を留保します。 インテルは、インテルが書面で明示的に同意した場合を除き、ここに記載されている情報、製品、またはサービスの適用または使用から生じる一切の責任を負わないものとします。 インテルのお客様は、公開されている情報を信頼したり、製品やサービスを注文したりする前に、最新バージョンのデバイス仕様を入手することをお勧めします。

*その他の名称およびブランドは、一般に各社の所有物である場合があります。

Intel HLS コンパイラーの廃止予定

- 最新の FPGA 高レベル設計機能、最適化、開発ユーティリティへのアクセスを維持するには、既存の設計を移行して Intel oneAPI Base Toolkit を使用します。

- Intel High Level Synthesis (HLS) コンパイラは、バージョン 23.4 以降では廃止される予定です。

- 移行に関するアドバイスについては、Intel oneAPI 製品ページをご覧ください。ご質問やご要望については、Intel High Level Design コミュニティ フォーラムをご覧ください。

新機能と機能強化

- Intel High Level Synthesis Compiler Pro Edition バージョン 22.4 には、次の新機能が含まれています。

- メンテナンスリリース。

- Intel HLS コンパイラー プロ・エディション バージョン 22.4 には新機能や機能強化はありません。

ソフトウェアの動作の変化

- このセクションでは、インテル HLS コンパイラー プロ・エディション バージョン 22.4 の機能がコンパイラーの以前のリリースから変更された点について説明します。

メンテナンスリリース。

- Intel HLS コンパイラー プロ・エディション バージョン 22.4 のソフトウェア動作に変更はありません。

インテル高位合成コンパイラー プロエディションの前提条件

- インテル HLS コンパイラー プロ・エディションは、インテル Quartus® Prime プロ・エディション デザインスイートの一部です。インテル HLS コンパイラーは、インテル Quartus Prime ソフトウェアのインストールの一部としてインストールすることも、個別にインストールすることもできます。使用するには、インテル Quartus Prime と追加のソフトウェアが必要です。

- システム要件、前提条件、ライセンス要件など、Intel Quartus Prime Pro Edition ソフトウェアのインストールに関する詳細な手順については、「Intel FPGA ソフトウェアのインストールおよびライセンス」を参照してください。

- Intel HLS コンパイラーには、Intel Quartus Prime に加えて次のソフトウェアが必要です。

C++ コンパイラ

- Linux では、Intel HLS コンパイラーには、GNU C++ ライブラリーとバイナリー ユーティリティー (binutils) を含む GCC 9.3.0 が必要です。

- このバージョンのGCCは、インテルHLSコンパイラーのインストールの一部として提供されます。インテルHLSコンパイラーをインストールすると、GCC 9.3.0が利用可能になります。 /gcc です。

- 重要: インテルHLSコンパイラーは、 /gcc ディレクトリをツールチェーン ディレクトリとして使用します。HLS 関連の設計作業はすべて、この GCC のインストールで行います。

- Windows の場合は、Microsoft* Visual Studio* Professional の次のいずれかのバージョンをインストールします。

- Microsoft Visual Studio 2017 プロフェッショナル

- Microsoft Visual Studio 2017 コミュニティ

- 最新の C++17 サポートについては、最新バージョンの Visual Studio 2017 を使用していることを確認してください。

- 重要: Intel HLS コンパイラー ソフトウェアは、ソフトウェアのエディションに指定されているバージョン以外の Microsoft Visual Studio のバージョンをサポートしていません。

シーメンス* EDA Questa® シミュレーション ソフトウェア

- Windows および RedHat Linux システムでは、Intel Quartus Prime ソフトウェア インストーラーから Questa® シミュレーション ソフトウェアをインストールできます。使用可能なオプションは次のとおりです。

- Questa Intel FPGA エディション

- Questa Intel FPGA スターターエディション

- Questa Intel FPGA Edition と Questa Intel FPGA Starter Edition の両方にライセンスが必要です。Questa Intel FPGA Starter Edition のライセンスは無料です。詳細については、Intel FPGA ソフトウェアのインストールとライセンスを参照してください。

- あるいは、Siemens* EDA ModelSim* SE または Siemens EDA Questa Advanced Simulator ソフトウェアの独自のライセンス バージョンを使用することもできます。

- Linux システムでは、Questa – Intel FPGA Edition および Questa – Intel FPGA Starter Edition には Red Hat* 開発ツール パッケージが必要です。

- Intel ソフトウェアがサポートするすべての ModelSim および Questa ソフトウェア バージョンの詳細については、Intel Quartus Prime Pro Edition のソフトウェアおよびデバイス サポート リリース ノートの EDA インターフェイス情報セクションを参照してください。

関連情報

- インテル高位合成コンパイラ入門ガイド

- サポートされているオペレーティングシステム

- Intel FPGA ソフトウェアのインストールとライセンスにおけるソフトウェア要件

- EDA インターフェイス情報 (Intel Quartus Prime Pro Edition)

既知の問題と回避策

- このセクションでは、Intel HLS コンパイラー プロ・エディション バージョン 22.4 に影響する既知の問題に関する情報を提供します。

| 説明 | 回避策 |

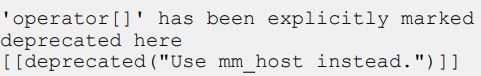

| 非推奨のクラス mm_master を使用すると、コンパイラは次のような警告メッセージを出力します。

このメッセージは、コードのどの部分を変更する必要があるかを示すものではありません。 |

非推奨のクラス mm_master に代わるクラス mm_host を使用すると、この警告メッセージを回避できます。 |

| (Windows のみ) パス名が長いディレクトリでデザインをコンパイルすると、コンパイルが失敗する可能性があります。

debug.logを確認する file 「見つかりませんでした file” エラーが表示されます。これらのエラーは、パスが長すぎることを示している可能性があります。 |

短いパス名を持つディレクトリでデザインをコンパイルします。 |

| (Windowsのみ) インテルQuartus Primeのインストールディレクトリのパスが長いと、インテルHLSコンパイラーのチュートリアルやexを正常にコンパイルして実行できない場合があります。ampルデザイン。

debug.logを確認する file 「見つかりませんでした file” エラーが表示されます。これらのエラーは、パスが長すぎることを示している可能性があります。 |

チュートリアルとexを移動するamp実行する前に、ファイルを短いパス名に変換してください。 |

| 説明 | 回避策 |

| OpenCL* をターゲットとし、HLS で記述されたライブラリは、OpenCL コードと HLS で記述されたライブラリ間のインターフェイスとしてストリームまたはパイプを使用できません。

ただし、HLSのライブラリでは、両方のエンドポイントがライブラリ内にある場合、ストリームまたはパイプを使用できます(例:ample、2 つのタスク関数を接続するストリーム)。 |

該当なし |

| ihc::maxburst パラメータを Avalon® メモリマップド ホスト インターフェイスに適用すると、シミュレーション中にデザインがハングする可能性があります。 | 該当なし |

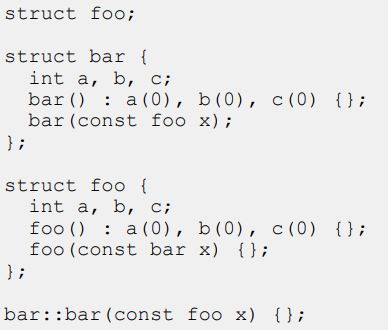

| まれに、コンストラクターがそれぞれ他のクラスのインスタンスを入力として必要とする 2 つのクラスがある場合、コンパイラがクラッシュすることがあります。

例えばampたとえば、次のコード スニペットをコンパイルすると、コンパイラがクラッシュします。

|

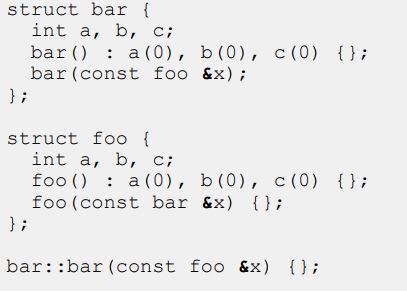

循環定義を作成しないようにしてください。代わりに、コピー コンストラクターでポインターまたは参照を使用します。

例えばample では、前のコード スニペットを次のコードに変換し、構造体をコンストラクターへの参照として渡します。

|

| OpenCL をターゲットとし、HLS で記述されたライブラリにより、ライブラリを含む OpenCL カーネルでより保守的な増分コンパイルが行われる可能性があります。 | 該当なし |

| ライブラリを開発するときに、後で #pragma で使用する値を定義する #define がある場合、fpga_crossgen コマンドは失敗します。

例えばampleの場合、次のコードはコンパイルできません

|

#pragma の代わりに pragma を使用してください。

例えばampleでは、次のコードは正常にコンパイルされます。

|

| -cコマンドオプションを使用してコンパイルとリンクを別々にすると、tagワークフローで、リンクファイルに-marchオプションを指定しない場合は、tage(または別の-marchオプション値を指定)の場合、リンクstagエラー メッセージの有無にかかわらず失敗する可能性があります。 | -cコマンドオプションを使用したコンパイルと-marchオプションの値が同じであることを確認してください。tageとリンクstage. |

| 説明 | 回避策 |

| 展開されたループまたは部分的に展開されたループ内で宣言された配列に hls_merge メモリ属性を適用すると、展開されたループの反復全体で配列のコピーがマージされます。

|

アンロールされたループでは hls_merge メモリ属性を使用しないでください。

展開されたループでメモリをマージする必要がある場合は、幅のマージ用に構造体型の配列を明示的に宣言するか、深さのマージ用により深い配列を宣言します。

|

| 関数メモリ内 View高レベルの設計レポートでは、一部の関数スコープのメモリが「最適化によって削除された」ように見える場合があります。 | なし。

とき file コンポーネントである関数とコンポーネントではない関数が含まれている場合、すべての関数スコープの変数は関数メモリリストペインにリストされますが、コンポーネントの変数のみが関数メモリに表示される情報を持っています。 View ペイン。 |

| 一部の高レベル設計レポートは、Microsoft Internet Explorer* では失敗します。 | 以下のブラウザのいずれかを使用して view 報告書:

• グーグルクローム* • マイクロソフトエッジ* • Mozilla* Firefox* |

| ループ View高レベル設計レポートの er には次の制限があります。

• ループではストールフリークラスタの挙動はモデル化されていない Viewループに表示される最終的なレイテンシ Viewストールフリー クラスターのレイテンシは、通常、設計の実際のレイテンシよりも悲観的 (つまり、高くなる) になります。 クラスタリングとストールフリークラスタの説明については、 データパスのクラスタリング の インテルハイレベル 合成コンパイラ Pro エディション ベスト プラクティス ガイド. • メモリまたは印刷ステートメントからの読み取りと書き込みによる停止はモデル化されていません。 • 反復回数が多いと(>1000)、ループのパフォーマンスが低下します。 Viewえー。 • ループ内で反復回数をゼロ(0)に指定することはできません。 Viewえー。 |

なし。 |

| Windows システムで生成された高レベル設計レポートの一部のレポート内のリンクは機能しません。 | Linux システムで高レベル設計レポートを生成します (つまり、コードをコンパイルします)。 |

| パケットを使用するストリーミングインターフェースで単一のac_intデータ型の構造体を使用する(ihc::usesPackets) ) 動作しません。

例えばampただし、次のコード スニペットは機能しません。

|

この組み合わせを設計で使用する場合は、次の制限に従ってください。

• 内部ac_intデータサイズは8の倍数でなければなりません • ストリームインターフェース型宣言では、 ihc::ビット/シンボル<8> 例えばampたとえば、次のコード スニペットは機能します。

|

| 説明 | 回避策 | |

| エンキュー関数呼び出しを使用してコンポーネントの高スループット シミュレーションを実行するときに、そのコンポーネントのすべての ihc_hls_enqueue 呼び出しの後に ihc_hls_component_run_all 関数を使用してエンキューされたコンポーネント呼び出しを実行しないと、次の動作が発生します。

• エミュレーションでは、キューに登録されたコンポーネント関数が実行されます。 • シミュレーションでは、キューに入れられたコンポーネント関数は実行されず、エラーや警告メッセージは表示されません。 |

キューに入れられたコンポーネント関数呼び出しを実行するには、そのコンポーネントのすべての ihc_hls_enqueue 呼び出しの後に ihc_hls_component_run_all 関数を使用するようにしてください。 | |

| ihc::launch_always_run でタスク関数を起動する | 最適化を取り除かないようにするには、while(1)を追加します。 | |

| タスクに適用された最適化属性を削除します | 影響を受ける関数にループし、対応する制御を適用する | |

| 関数。 | 関数の代わりにwhile(1)ループにプラグマを追加します。 | |

| 次のコードで例ample の場合、関数に適用された属性は無視されます。高レベル設計レポートでは、このタスクに対して、要求された II 1 ではなく II 4 が表示されます。 | 次のコード例amp以前のコードにこの変更を実装する方法を示します。amp上: | |

|

|

|

| 複数の HLS コンポーネントを含む Cyclone® V プロジェクトの場合、i++ コマンドを使用してプロジェクトをハードウェアにコンパイルすると (i++ -march=CycloneV)、エラーが発生する可能性があります。

エラー テキストはプロジェクトによって異なりますが、エラー シグネチャは、Verilog 構文が間違っているために Intel Quartus Prime コンパイルが失敗したことを示します。モジュールは、Intel Quartus Prime コンパイラが見つけられない関数を使用しようとしています。 |

この問題が発生した場合は、各 HLS コンポーネントを個別のプロジェクトに配置します。 | |

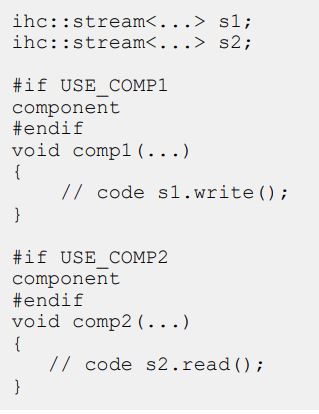

| 複数のコンポーネントを含む一部のデザインをコンパイルすると、ストリームの再利用に関するエラーが発生します。 | この問題が発生した場合は、デザイン内の各コンポーネントを個別にコンパイルします。各コンポーネントを個別にコンパイルできるようにするには、コードにマクロを追加する必要がある可能性があります。 | |

| 次の例を検討してくださいamp上: | ||

|

||

インテル高位合成コンパイラー プロ・エディション リリースノート アーカイブ

このユーザーガイドの最新版および以前のバージョンについては、Intel HLS コンパイラー プロ・エディションのリリースノートを参照してください。ソフトウェア バージョンが記載されていない場合は、以前のソフトウェア バージョンのリリースノートが適用されます。

インテル HLS コンパイラー プロ・エディション バージョン 22.4 リリースノートのドキュメント改訂履歴

| ドキュメントバージョン | インテル Quartus Prime バージョン | 変更点 |

| 2022.12.19 | 22.4 | • 初回リリース。 |

ドキュメント / リソース

|

インテル高位合成コンパイラー プロエディション [pdf] 説明書 バージョン 22.4、バージョン 23.4、高位合成コンパイラ プロ エディション、高位合成コンパイラ プロ エディション |